# SIEMENS

YOUR CONTACT FOR ENQUIRY IS:MR C SHILE

SUNBURY-ON-THAMES

TEL (09327) 85691

**Data Book 1976/77**

MOS-Circuits **MOS-Circuits**

| Contents · Summary of Types · General Information |

|---------------------------------------------------|

|                                                   |

|                                                   |

| MOS-Circuits for Entertainment Applications       |

|                                                   |

|                                                   |

| MOS-Circuits for Consumer Applications            |

|                                                   |

|                                                   |

|                                                   |

| MOS-Circuits for Industrial Applications          |

|                                                   |

|                                                   |

| List of Sales Offices                             |

|                                                   |

# SIEMENS

MOS-Circuits

Data Book 1976/77

Published by Siemens AG, Bereich Bauelemente, Produkt-Information, Balanstraße 73, 8000 München 80.

For the circuits, descriptions, and tables indicated no responsibility is assumed as far as patents or other rights of third parties are concerned.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Offices of Siemens . Aktiengesellschaft in the Federal Republic of Germany and Berlin (West) or the Siemens Companies and Representatives abroad (see list of Sales Offices).

Contents  $\cdot$  Summary of Types  $\cdot$  General Information

# **Table of Contents**

| 1.       | General information on MOS-circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page     |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1.     | Introduction to MOS-technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 9      |

| 1.2.     | rabrication of MOS-transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11       |

| 1.3.     | MOS fabrication processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12       |

| 1.3.1.   | Metal gate technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 13     |

| 1.3.2.   | Silicon gate technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 14     |

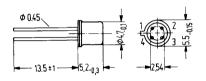

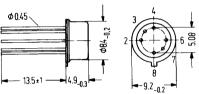

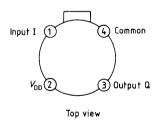

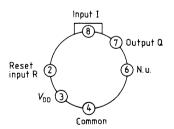

| 1.4.     | Package mounting instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 17     |

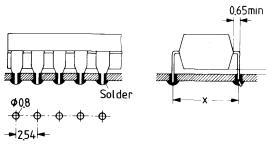

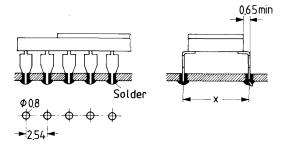

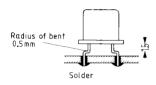

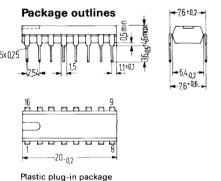

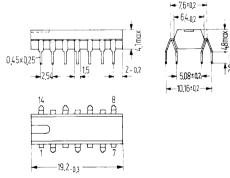

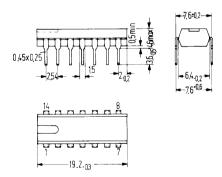

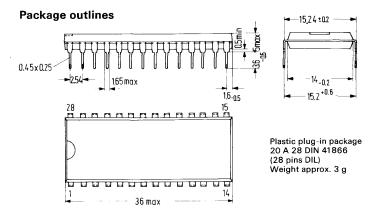

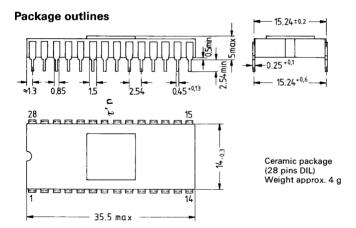

| 1.4.1.   | Plastic and ceramic plug-in packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 17     |

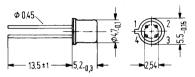

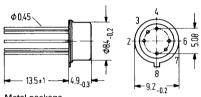

| 1.4.2.   | Package 5H8 DIN 41873 and similar packages with 8, 10 and 12 pins .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 17     |

| 1.5.     | Protection measures for MOS-circuits .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 19     |

| 1.6.     | Type nomenclature for MOS-circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 19     |

| 1.6.1.   | Siemens type nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 20     |

| 1.6.2.   | PRO ELECTRON type nomenclature .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 20     |

| 1.7.     | Quality data for MOS-circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 20     |

| 1.7.1.   | Warranty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 21     |

| 1.7.3    | AQL – figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 21     |

| 1.7.3.   | Average outgoing quality (AOO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 21     |

| 1.7.4.   | Average outgoing quality (AOQ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 22     |

|          | Random sample testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 22     |

| 1.7.5.   | Rejections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 22     |

| 1.7.0.   | AQL random sample testing procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 23     |

| 1.0.     | Glossary of abbreviations used for MOS-circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 24     |

| 2.       | MOS-circuits for entertainment applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| S 175 A  | A Triple analog-data memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20       |

| 5 551    | Message decoder ) for FM car radio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24       |

| S 552    | Area decoder road traffic information service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34       |

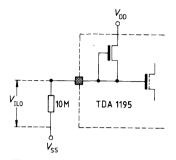

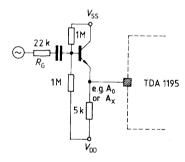

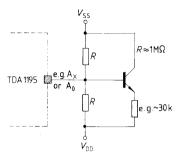

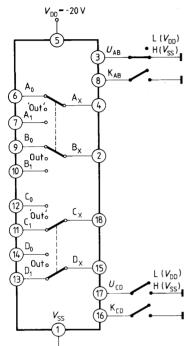

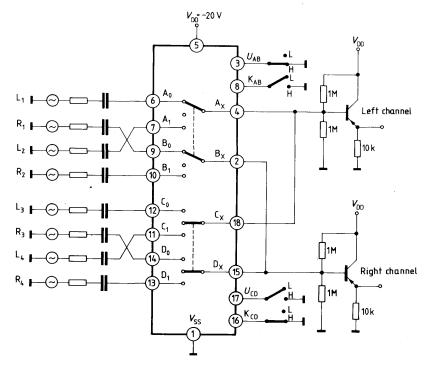

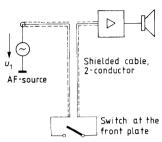

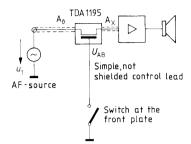

| TDA 11   | 95 AF selector switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46<br>54 |

|          | The second state of the se | 54       |

| 3.       | MOS-circuits for consumer applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

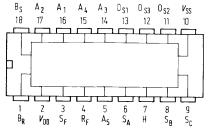

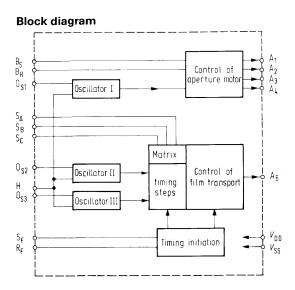

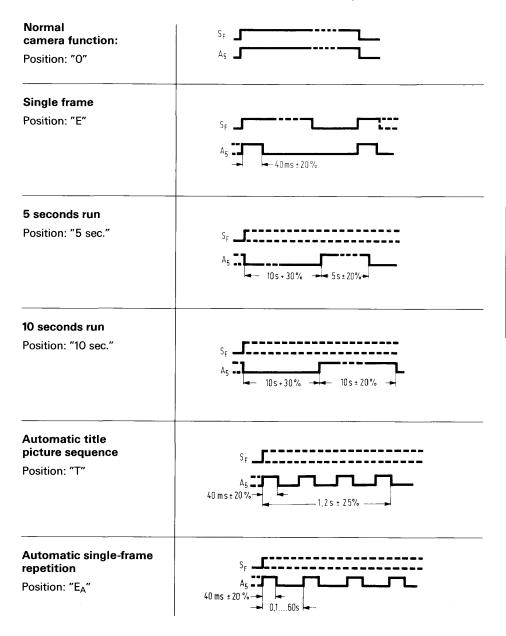

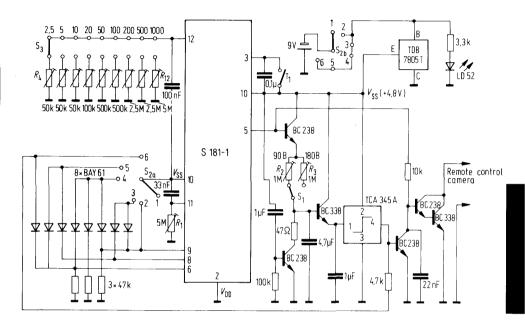

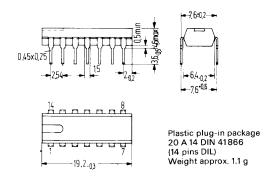

| S 181-   | 1 Movie camera controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

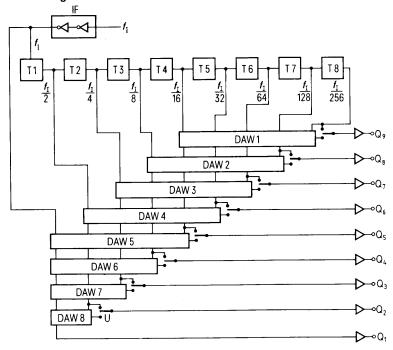

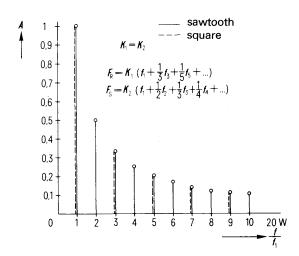

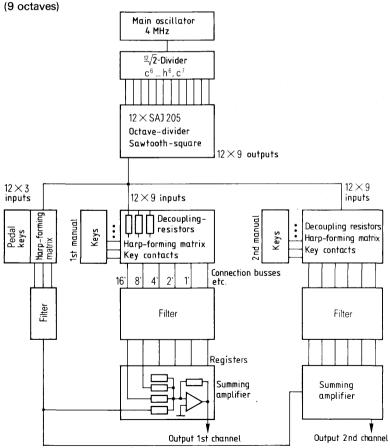

| SAJ 20   | Staircase generator for electronic organs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67       |

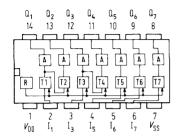

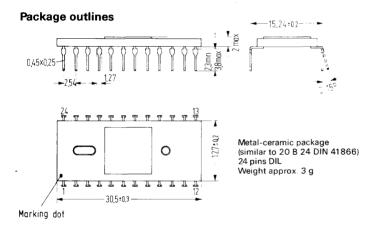

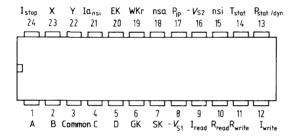

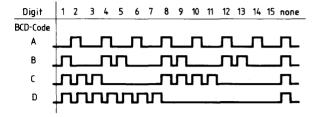

| SA.J 41  | O, SAJ 410 A 7-stage frequency divider for electronic organs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75       |

| J. 10 TI | S S S S S S S S S S S S S S S S S S S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2/       |

| 4.             | MC    | os-      | circ  | cui | ts 1     | for | in   | dust          | rial           | ар    | plic | ati     | ons  | ;            |          |              |      |      |      |        |       |        |     |       |     | F | Page |

|----------------|-------|----------|-------|-----|----------|-----|------|---------------|----------------|-------|------|---------|------|--------------|----------|--------------|------|------|------|--------|-------|--------|-----|-------|-----|---|------|

| S 12           | 0Δ:   | 3        |       |     |          |     | . F  | ush-          | but            | ton   | dia  | ller    |      |              | 1        | for          | р    | ush  | ı-b  | utte   | on    |        |     |       |     |   | 89   |

| S 12           | 1 B   | <b>.</b> | •     | •   | •        | •   | Ē    | ush-          | -but           | ton   | me   | mo      | rv   |              | Ì        | tel          | eph  | on   | es   |        |       |        |     |       |     |   | 99   |

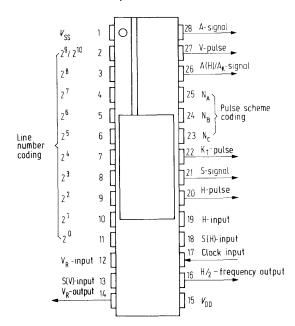

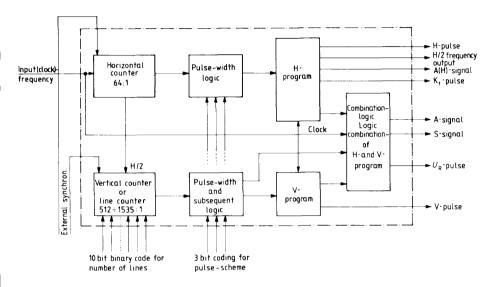

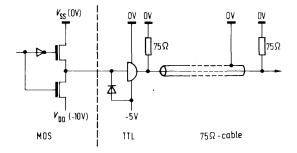

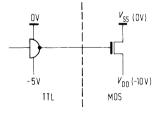

| C 17           | ם ו   | •        | •     | •   | •        | •   | ٠,   | /iden         | nu             | lse   | ger  | era     | tor  |              | ΄.       |              | ٠.   |      |      |        |       |        |     |       |     |   | 108  |

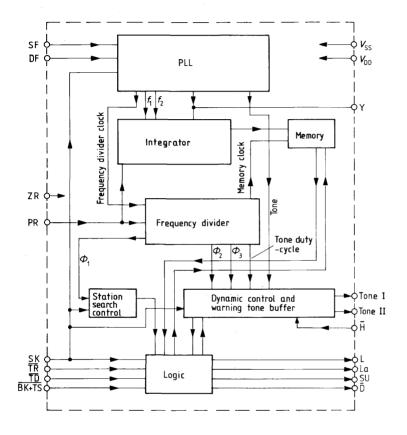

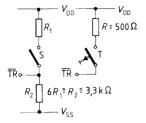

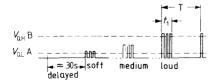

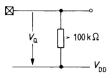

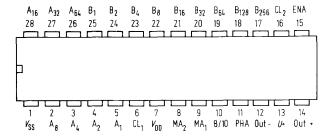

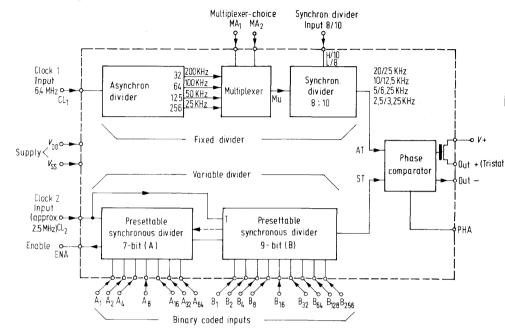

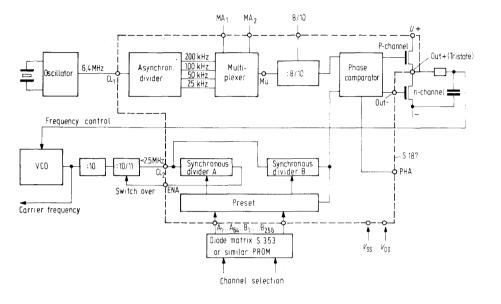

| 0 1 /<br>C 1 Q | 7     | •        | •     | •   | •        | •   |      | liaite        | al fr          | ear   | ieno | CV S    | svnt | hes          | size     | r .          |      |      |      |        |       |        |     |       |     |   | 118  |

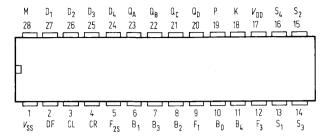

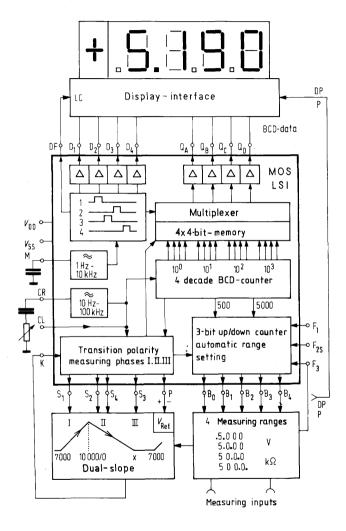

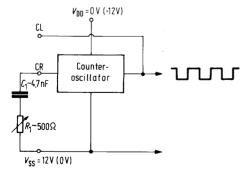

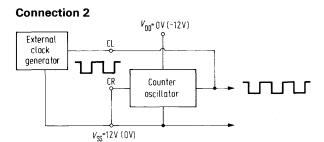

| O 10           |       | •        | •     | •   | •        | •   |      | )igite        | ıı ıı          | nulti | ime  | ter     | IC.  |              |          |              |      |      |      |        |       |        |     |       |     |   | 129  |

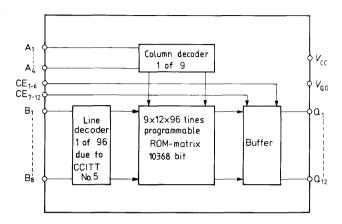

| 0 10           |       | •        | •     |     |          | •   |      | ngite<br>n ki | hit [          | RON   | M    |         |      | •            |          |              |      |      |      |        |       |        |     |       |     |   | 143  |

| 2 PC           | 101   | ٠.       |       | >=  |          | •   | ٠ .  | totic         | fro            | COL   | vi . | , di    | vide | r 1          | იი       | ص            | 1    |      | -    |        |       |        |     |       |     |   | 144  |

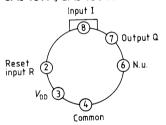

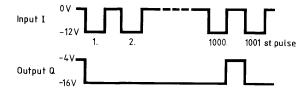

| SAJ            | 131,  | SAC      | ) I ( | 30  | ).<br>). | ٠,  |      | otatio        | fra            | que   | 200  | , div   | ida  | " ·<br>r 1 ( | ากก      | . 1          | wil  | he   | yte  | rna    | al re | ese    | t.  |       | _   |   | 144  |

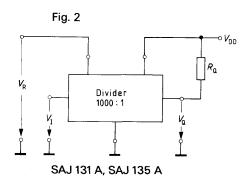

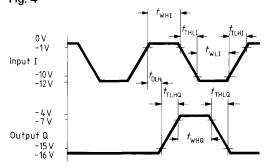

| SAJ            | 131   | Α,       | SAL   | J   | 35       | . А | . 3  | Static        | ; II e         | que   | лсу  | ار الله | idar | 100          | 100      | in.          | ion  | in   | nlo  | nte    | atio  | n t    | och | nic   |     | - | 147  |

| SAJ            | 131   | -I, S    | βAJ   | 13  | 35-<br>  | ١.  |      | static        | rre            | que   | ncy  | aiv     | iuer | 100          | )U.      | 1 III<br>1 : | 1011 | -111 | ibic | 21116  | atio  | n t    | ook | nic   | uc  |   | 147  |

| SAJ            | 131 / | ۹-I,     | SA.   | J 1 | 35       | A-  | 1. 3 | Static        | tre            | que   | ncy  | aiv     | ıaer | 100          | <i>.</i> | ı ın         | IOI  | -111 | pia  | 11 ILC | טווכ  | 71 I L | CCI | IIIIC | ļuc |   |      |

| SAJ            | 141   |          |       |     |          |     |      | 1000          | ) : <b>1</b> , | , 10  | 0 :  | 1, 1    | 0 :  | 1 di         | vid      | er.          |      |      | ٠    |        |       | ٠      | •   | •     | ٠   | • | 150  |

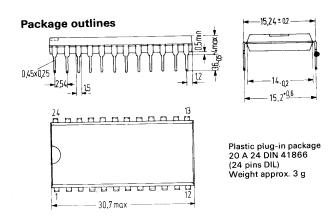

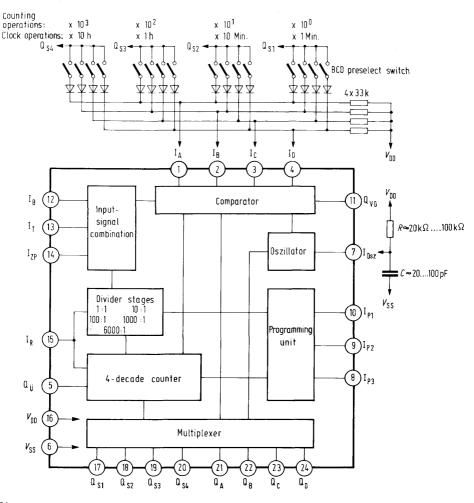

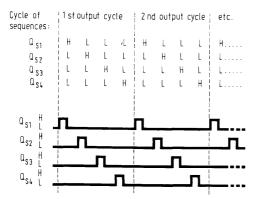

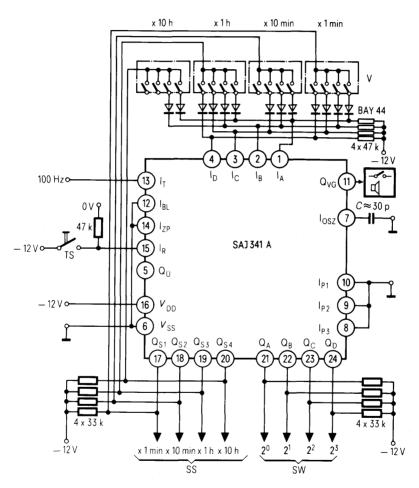

| SAI            | 341   | Δ        |       |     |          |     | . 4  | 1-ded         | cade           | e co  | ount | ter/    | cloc | k l          | С.       |              |      |      |      |        |       |        |     |       |     |   | 155  |

#### 1.1. Introduction to the MOS technology

MOS is a technology used for the fabrication of largescale integrated digital circuits. MOS is the abbreviation of **Metal-O**xide-**S**ilicon, which also explains the principle construction of a transistor (see fabrication of the MOS-transistor, page 11).

The main advantages of the MOS technology are:

- simple construction of the transistors

- high density of integration

- extremely low power consumption of the transistors

On a silicon chip with an area of no more than 30 mm², up to 20 000 transistors can be integrated today. By 1980 it will be possible to realize 100 000 transistors on a single chip. The increasing level of integration causes a growing proportion of the development- and fabrication-value to be shifted from the equipment manufacturer to the component manufacturer. Siemens, as a component manufacturer, offers her customers the chance of a joint development of application-specific MOS-circuits, in addition to supplying standard circuits. There is also a possibility of Siemens second-sourcing a specific circuit already used by the customer. A requirement for this is the compatibility of technology. The diagram on page 10 shows, at which development steps of an MOS project a

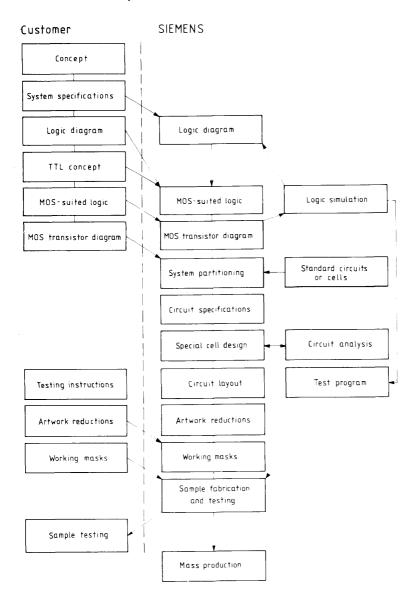

The diagram on page 10 shows, at which development steps of an MOS project a cooperation between the customer and Siemens is possible.

Possible cooperation of Siemens with the customer at the various stages of an MOS-circuit development

# 1.2 Fabrication of the MOS transistor (p-channel)

| n - substrate | Starting material: n-conducting silicon                                                            |

|---------------|----------------------------------------------------------------------------------------------------|

|               | Growing a layer of silicon-oxide (0,5 $\mu$ m)                                                     |

| 777 F772      | Using photo-lithography and a first mask, windows for the p-regions source and drain are produced. |

| p n p         | Diffusion of the p-regions                                                                         |

|               | Deposition of a layer of thick oxide (1,2 $\mu$ m)                                                 |

|               | Using the second mask, windows for the three contacts are etched                                   |

|               | Growing the gate oxide (0,1 $\mu$ m)                                                               |

|               | Removal of the gate oxide covering the source and drain regions by means of a third masking step   |

|               | Vapor deposition of aluminum as contact- and interconnect-metal                                    |

Using a final fifth mask, the connection pads used for bonding are exposed.

(fourth masking step)

#### 1.3. MOS fabrication processes

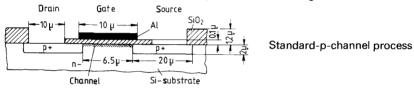

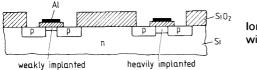

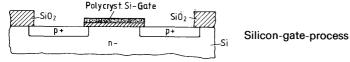

Basic differences of the various fabrication techniques can be found in the construction of the gates and the type of doping of the substrate. The gate electrodes of the transistors are made either with aluminum metal or silicon. Therefore, these techniques are called *Metal-Gate technique* or *Silicon-Gate-technique*, respectively. Until 1975, n-type substrate material was used in all fabrication processes. Consequently, the resulting transistor channels were of the p-type and this process was called *p-channel process*. The counterpart is the *n-channel process*. Both processes will be explained in the following paragraphs.

A further distinguishing characteristic is the state of conduction of the integrated transistors. Without a voltage applied to the gate, a transistor may be conducting or non-conducting.

If conducting, it is called a depletion transistor. This means that an increasing voltage applied between gate and source will tend to narrow-down the channel by gradually depleting it of charge carriers. The resistance of the conducting path rises from a typical value of about  $10~\text{k}\Omega$  to  $10^{15}~\Omega$ . This mode of operation is called "depletion mode". The opposite occurs with a transistor of the so-called enhancement type. In this type of transistor the conductive channel is formed and enhanced by an increase of the gate-source voltage. Therefore, this mode of operation is called "enhancement mode".

A channel is a conducting path between source and drain, caused by a charge inversion in the upper layer of the substrate, underneath the gate oxide. This inversion usually involves a depth of about 10nm, equal to 100 Angström. The inversion layer is p-conducting for the p-channel process and n-conducting for the n-channel process.

#### 1.3.1. Metal-gate-technologies

#### p-channel high-voltage-process

This process still remains to be the standard process. Its main advantages are the simplicity of the process and the resulting relatively low fabrication costs.

The process, which has been used for production since 1967, is very well controlled by the manufacturers with respect to yield and reliability. The high supply voltages result in a high noise immunity, which is of great benefit especially to custom circuits in industrial applications.

For standard circuits, the high supply voltage constitutes a disadvantage because the circuits are not compatible with bipolar circuit families.